Product Summary

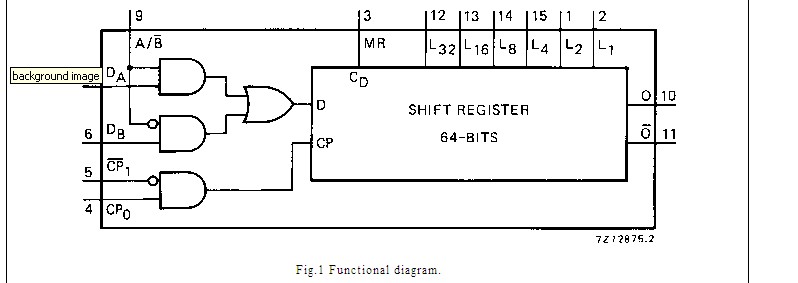

The HEF4557BP is a 1-to-64 bit variable length shift register length may be programmed to be any number of bits between 1 and 64. The number of bits selected is equal to the sum of the subscripts of the enabled length control inputs (L1, L2, L4, L8, L16 and L32) plus one. Serial data may be selected from the DA or DB data inputs with the A/B select input. The HEF4557BP feature is useful for recirculation purposes. Information on DA or DB is shifted into the first register position and all the data in the HEF4557BP is shifted one position to the right on the LOW to HIGH transition of CP0 while CP1 is LOW or on the HIGH to LOW transition of CP1 while CP0 is HIGH. A HIGH on master reset (MR) resets the register and forces O to LOW and O to HIGH, independent of the other inputs

Parametrics

HEF4557BP absolute maximum ratings: (1)Minimum clock pulse frequency 5 fmax: 2.5, 5 MHz; (2)Minimum clock pulse frequency 10 fmax: 7, 14 MHz; (3)Minimum clock pulse frequency 15 fmax: 10, 20 MHz; (4)Minimum reset spulse width HIGH 5 tWMRH: 150, 75 ns ; (5)Minimum reset spulse width HIGH 10 tWMRH: 70, 33 ns ; (6)Minimum reset spulse width HIGH 10tWMRH: 50, 25 ns.

Features

HEF4557BP features: (1) The IC04 LOCMOS HE4000B Logic Family Specifications HEF, HEC; (2) The IC04 LOCMOS HE4000B Logic Package Outlines/Information HEF, HEC.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

HEF4557BP,652 |

NXP Semiconductors |

Counter Shift Registers 1-TO-64 BT VAR LNGTH |

Data Sheet |

|

|

||||||||||||

|

HEF4557BPN |

NXP Semiconductors |

Counter Shift Registers 1-TO-64 BT VAR LNGTH SHFT REG |

Data Sheet |

Negotiable |

|

||||||||||||

(China (Mainland))

(China (Mainland))